横浜市経済局企業誘致・立地課は12月21日、Samsung Electronicsが横浜市西区の「みなとみらい21地区」に半導体の次世代パッケージング技術の研究拠点「Advanced Package Lab」を新設すると発表した。

Samsungの投資規模は今後5年間で400億円(約3500億ウォン)を上回ると予想され、政府がその半分、最大200億円の助成金を支給する。

「横浜はパッケージ関連企業が多く、優秀な大学と人材もあるため、業界、大学、研究機関などと協力するのに適した場所の一つだ」としている。

経産省は同日、ポスト5G情報通信システム基盤強化研究開発事業の開発テーマ「高性能コンピューティング向け実装技術」に関して、採択審査委員会での審査を経て、日本サムスンを採択先として決定したと発表した。

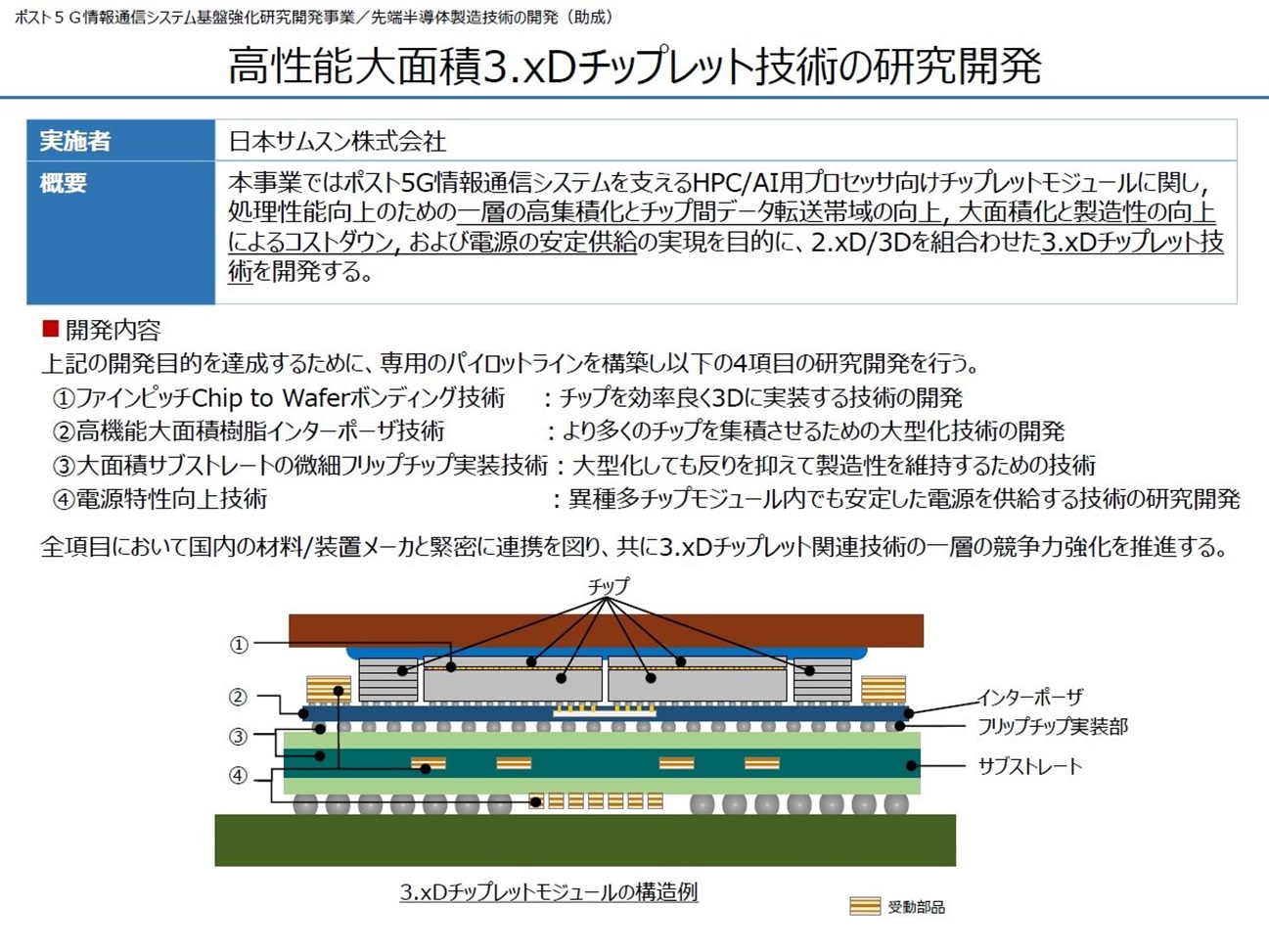

日本サムスンの採択事業テーマは「高性能大面積3.xDチップレット技術の研究開発」で、ポスト5G情報通信システムを支えるHPC(高性能コンピューティング)/AI(人工知能)用プロセッサ向けチップレットモジュールに関し、処理性能向上のためのさらなる高集積化とチップ間データ転送帯域の向上、大面積化と製造性の向上によるコストダウンおよび電源の安定供給の実現を目的に、2.xD/3Dを組み合わせた「3.xDチップレット技術」を開発するとしている。

この開発目的達成のため、同社は専用のパイロットラインを構築。チップを効率良く3Dに実装する技術「ファインピッチChip to Waferボンディング」、より多くのチップを集積させるための大型化技術「高機能大面積樹脂インターポーザ」、大型化しても反りを抑えて製造性を維持するための技術「大面積サブストレートの微細フリップチップ実装技術」、異種多チップモジュール内でも安定した電源を供給する技術「電源特性向上技術」の研究開発を、日本国内の材料/装置メーカーと連携を図りながら行っていく方針。

次世代半導体の国産化をめざす共同出資会社「Rapidus」が北海道に建設する新工場に対しては、政府は「ポスト5G情報通信システム基盤強化研究開発事業」の採択先として、2回計3300億円を補助している。

2023/4/26 政府、ラピダスに2600億円の追加補助

他に、半導体支援として下記の2つがある。

1) 経済産業省の「半導体の安定供給確保のための取組に関する計画(供給確保計画)」 概要と、承認済みの計画(今回を含め18件)

2) 特定半導体生産施設整備等計画認定制度があり、これまでTSMC、キオクシア、マイクロンメモリ(2件)が多額の助成金を認められている。

コメントする